# 金屬氧化半導體場效電晶體 MOSFET

### (一) 關於電晶體

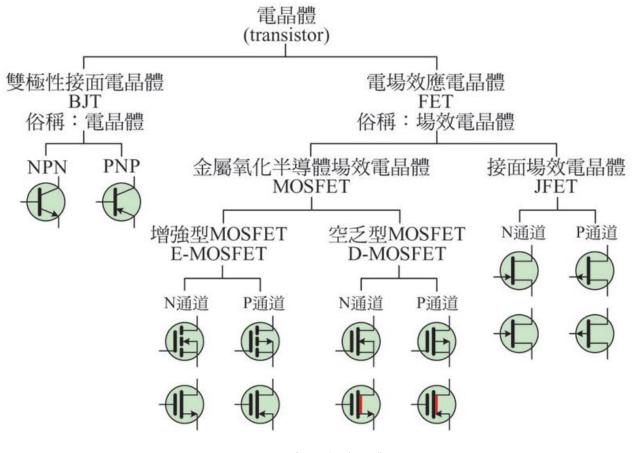

電晶體主要分為兩大類:雙極性電晶體(Bipolar Junction Transistor, BJT)和場效應電晶體(Field Effect Transistor, FET)。場效應電晶體又分為 金屬氧化半導體場效電晶體(MOSFET)和接面場效電晶體(junction FET, JFET)如下(圖 1),其中 MOSFET 依其通道形成方式又可分成增強型(Enhancement-Type)與空乏型(Depletion-Type)兩種。

場效應電晶體的三個極則分別是源極 (Source)、閘極 (Gate) 和汲極 (Drain)。

(圖1) 常見的電晶體分類

#### (二) 關於 MOSFET

MOSFET 應該是人類使用最多的電晶體種類,特別是在電腦及通訊相關的電子設備中,大量的這種電晶體開關幫助我們處理、運算及記憶大量的數據。由於MOSFET 的結構特別適合被縮小化,而且功率需求也小,在同一晶片上製作上千萬個電晶體開關變得可行。

#### (三) MOSFET 的操作原理

MOSFET 控制通道的方式和JFET 不同,但元件特性有許多相同之處。這裡我們以n通道MOSFET

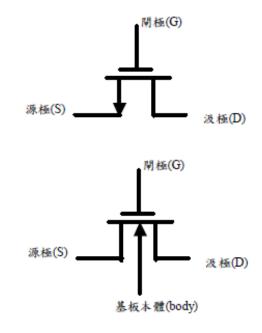

(簡稱NMOS)為例來介紹他的構造與原理。(圖2a)為一典型的NMOS 的結構示意圖。閘極是由金屬、氧化層和半導體依序疊在一起所形成類似電容的結構(氧化層當做介電質),故命名為金氧半場效電晶體。閘極只要加上足夠的正電壓,即可在半導體內靠近氧化層的介面上,吸引足夠多的導電電子形成通道,使源極與汲極的n+區導通。故控制閘極的電壓,等效上就是控制氧化層內的電場,就可以控制源極與汲極之間的導電特性。基板本體(body)有時也會接出一隻腳,使MOSFET 變成四隻腳的元件,在大部分的應用中,基板本體會和源極接在一起,使源極、汲極和基板本體間的pn 接面永遠是不導通的,如此MOSFET 就變成和JFET 類似的三隻腳元件。(圖2b)包括三隻接腳與四隻接腳的NMOS 電路符號。

(圖 2a) 為一典型的 NMOS 的結構示意圖

(圖2b)三隻接腳與四隻接腳的NMOS電路符號

由於 MOSFET 中,導電電子是在靠近介面的通道運動,因此氧化層與半導體接面必須製作得非常平整。現代的半導體技術能夠在矽晶圓的表面形成結構緻密的二氧化矽(SiO2)層,而且介面的品

質可以有效地被控制,故常用的MOSFET元件均是以矽晶圓做基板材料。

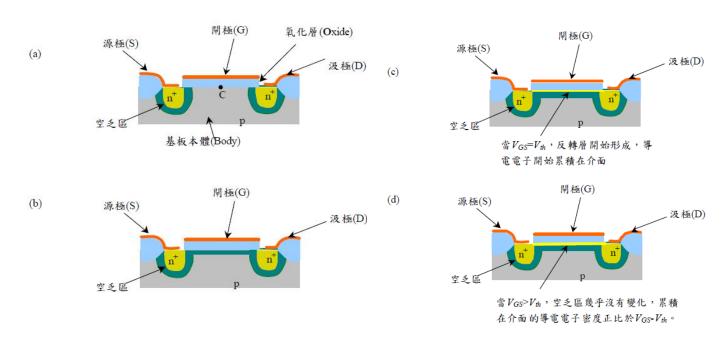

下面我們將較仔細的介紹n通道MOSFET 的工作原理以及元件在不同偏壓情形的變化。當閘極沒加偏壓(相對於基板本體或與之連結之源極),源極與汲極間只是像兩個反向串接的pn 接面,互不導通,NMOS 在所謂的截止(cut off)狀態,如(圖3a),其中還顯示了n+型源極與汲極各和p\型基板間pn 接面的空乏區。

圖3 不同閘極偏壓下,空乏區與通道形成之示意圖。 (a) $V_{GS}$ =0, (b)  $V_{GS}$ < $V_{th}$ , (c)  $V_{GS}$ = $V_{th}$ , (d)  $V_{GS}$ > $V_{th}$ 。

在閘極與基板本體(和源極相接)間慢慢加上正電壓,由於閘極的結構類似電容,閘極的金屬導體會堆積一些正電荷,而在氧化物絕緣層另一邊,則會吸引等量的負電,我們可以看成是吸引了導電電子,但電子在很短時間內即被多數載體電洞復和了,或者是電洞被閘極的正電荷趕跑了,不管哪一種看法,結果都是在靠近氧化層的p型半導體內形成空乏區,所帶的負電都來自電洞被游離的受子摻雜,如(圖3b),這裡先討論汲極與源極電位差很小的情形。源極與汲極間仍然不導通,NMOS在截止區。如果閘極的正電壓持續增加,到達一特定的臨界電壓 Vih(threshold voltage),在氧化層與半導體的介面會開始出現導電電子層,如(圖3c)。以後再增加的閘極電壓就不再用來改變空乏區的大小,而是用來增加導電電子層的電子數目,如(圖3d)。這時源極與閘極可藉由此導電電子層形成之通道導通。由閘極的電壓變化,可以將原本p型半導體,轉變成具導電電子的n型通道,此導電通道我們稱為反轉層(inversion layer)。

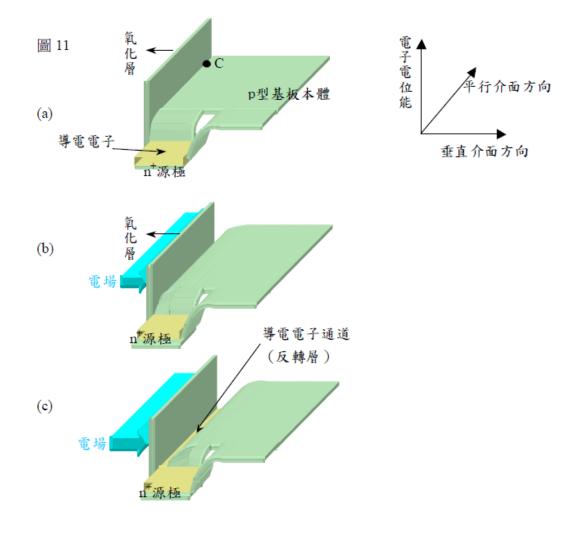

閘極電壓加到什麼程度反轉層才會形成呢?這必須考慮在半導體靠近氧化層介面的電子電位能受到閘極電壓影響產生的變化。假設沒有加閘極電壓時,氧化層和半導體中均無電場,電子在p型半導體中(遠離源極和汲極處)的電位能分佈應是平的,如圖4(a),圖中z軸方向代表電子電位能,另兩軸是標示在半導體中的位置。電子不喜歡處在氧化層中,也就是說那裡的電位能較高,故在進入氧化層的介面上有一個像牆一樣很高的位障,阻止電子進入氧化層。靠近源極或汲極的n+半導體處,電子電位能較在p型半導體中為低,這裡讀者可以參較在pn二極體中的討論。圖4只畫出靠近源極附近的電位能分佈狀況,在汲極和源極電位差不大的情形下,在汲極附近的電位能分佈狀況也類似。介面通道區的電子電位能太高,導電電子被侷限在源極與汲極的n+區,不能互相導通。

(圖4) NMOS 中,對於不同閘極偏壓,電子電位能在半導體中的分佈圖。 (a)VGS=0,(b)  $VGS<V_{th}$ ,(d)  $VGS>V_{th}$ 。導電電子無法進入氧化層,故氧化層用一極高的位障表示。

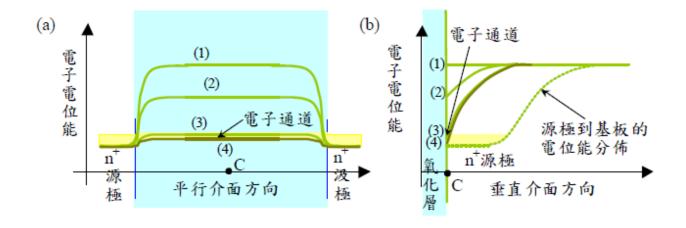

對閘極開始加正電壓時,氧化層中會有一朝向半導體基板的電場,如(圖4b)所示,電子在閘極金屬的電位能會變低,靠近介面的p型半導體區的電子電位能也會被往下拉,電位能面彎曲的部分就是空乏區的部分。當閘極的電壓足夠高,即超過Vth 時,靠近介面的半導體區的電子電位能會下降到使源極(n+區)中的導電電子能夠流入通道區,如(圖4c)所示,形成反轉層,源極與汲極間遂能導通。(圖5a)是在不同的閘極偏壓,靠近氧化層的半導體中,電子電位能沿著源極、通道中點C到汲極的分佈改變;(圖5b)則是由C點、沿著和介面垂直方向,朝向基板方向的電子電位能變化,虛線是由源極到p型半導體基板的電位能變化。

通道中點C 在(圖3a)及(圖4a)中也有標出來。從圖5中很容易看出通道區和源極電子電位能的差別,而閘極電壓就是用來調整在氧化層與半導體介面通道的電子電位能。這裡還有一點要說明,在 Vos 超過Vih 後,再增加的電壓除了持續在閘極金屬層有正電荷儲存外,在半導體區也必須增加等量的負電荷,由於此時反轉層已形成,負電荷很容易由源極進入通道,所費之能量遠較改變空乏區產生負電荷來得小,因此空乏區寬度就不再變化了。

(圖5) NMOS中,對於不同閘極偏壓,電子電位能在半導體中,(a)沿著源極、通道中點C到汲極 (b)由C 點、沿著和介面垂直方向,朝向基板方向的分佈圖,圖中之虛線是由源極到p型半導體基板 的電位能變化。 (1)VGS=0,(2) VGS=Vth,(3) VGS=Vth,(4) VGS=Vth。

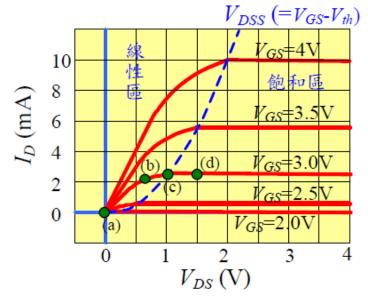

瞭解了 NMOS的操作原理,下面我們可以開始討論他的電流電壓的特性。圖6是不同閘極偏壓 (VGS)的ID 對VDS 曲線,這個圖例中NMOS 的臨界電壓VIh 為2V,可以和圖7比較,JFET 和MOSFET 的 特性相當類似。當VGS>VIh時,源汲極間開始導通,考慮源極和汲極電位差不大的情形,反轉層的電子密度約和(VGS-VIh)成正比,因此通道的電阻和(VGS-VIh)成反比,故在VDS 很小的區域, ID 對VDS 的關係幾乎為一條直線,而且對相同的VDS,(VGS-VIh)愈大則導電電子愈多,ID 愈大。

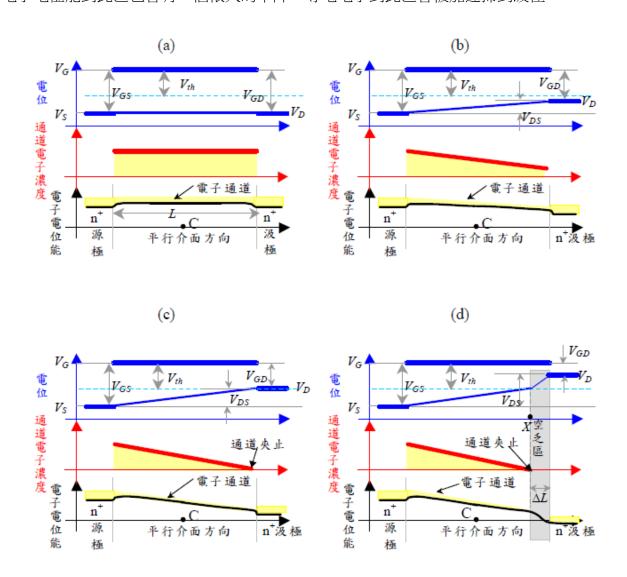

(圖6) 不同單極偏壓(VGS)的ID 對VDS 曲線,這個NMOS 的臨界電壓Vth 為2V。

當Vos 變大時,和JFET 的情形類似,Io 對Vos 的曲線也會向下彎,原因和JFET 也有類似之處。考慮Vos 固定在3V 的情形,Vos 很小時,整個通道上的電位差不多,閘極金屬到通道上任一點的電位差也都一樣,通道上的導電電子密度分佈很均勻,如(圖7a)所示。圖7是當Vos(>Vth)固定時,對於不同Vos,沿著通道的電位、導電電子濃度及電位能變化曲線。當Vos 增大時,通道上的電位會由源極向汲極方向變高,閘極金屬到通道的電位差在靠近汲極處較小,因此在靠近汲極處通道的導電電子密度變小。(圖7b)是Voo(=Vos-Vos)> Vth 的情形,靠近汲極的通道電子密度較小,整個通道的電阻較Vos 很小時為大,故Io 對Vos 的曲線會向下彎曲。當Voo= Vth,如(圖7c),最靠近汲極的反轉層消

失,通道被夾止。如果VDS 繼續增加,VGD 變得比VIh 小,靠汲極被夾止的區域 $\Delta L$  會略微變大,形成空乏區,但 $\Delta L << L$ ,如(圖7d)所示,反轉層消失的點X 的電位符合VGX = VIh,和VDS 無關,也就是說反轉層兩端之電位差VXS 不隨VDS 改變,而且反轉層之電子濃度分佈與尺寸大小也不隨VDS 改變,故通過之電流ID 不隨VDS 改變。靠近汲極通道夾止後再增加的VDS,大部分都落在被夾止部分的空乏區,電子電位能到此區也會有一個很大的下降,導電電子到此區會被加速掃到汲極。

(圖7) 當NMOS 之VGS(>Vth)固定時,對於不同VDS,沿著通道的電位、導電電子濃度及電位能變化曲線。(a) VDS=0,(b) VGD(=VGS-VDS)>Vth,(c) VGD=Vth,(d)VGD<Vth。

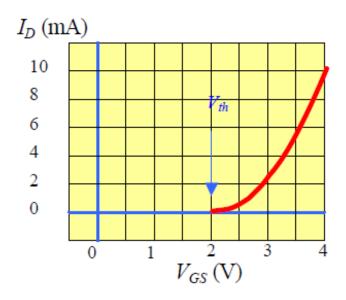

(圖6)中標示VGS=3.0V 的曲線上,標有(a)、(b)、(c)與(d)四點,分別對應 (圖7)中相同編碼圖形的偏壓情形。(a)和(b)的偏壓並不會使反轉層消失,通道和電阻類似,Io 隨Vos 增加,稱為歐姆區或線性區;在Vos 比(c)點大的區域,Io 幾乎不隨Vos 改變,稱為飽和區或恆流區。歐姆區與飽和區的交界電壓Voss 必需符合VGD=VGS-VDSS = Vth,即VDSS =VGS-Vth,VDSS 隨VGS 變大,如(圖6)中之虛線。和 JFET 類似,MOSFET 是利用閘極偏壓控制源汲極間導通特性的元件,而且兩者之電特性也十分相像,不過一般而言MOSFET 的閘極漏電流會比JFET小。(圖8)是NMOS在飽和區的典型轉換特性曲線。很容易可以發現JFET 在沒加偏壓(VGS=0)時是導通的,而NMOS 在沒加偏壓時是不導通的。通常我們稱前者為空乏型(depletion mode)FET,因為要改變現有導通的狀況,必須在閘極施加偏壓,使得通道被"空乏"掉;後者則稱為增強型(enhancement mode)FET,因為要改變現有導通的狀況,必須在閘極施加偏壓,使得通道被"增強"出來。MOSFET 也可以設計成空乏型的元件,只要製作時在靠近

介面的半導體中直接摻雜製作出通道,例如NMOS 就加入n 型摻雜即可,如此在沒閘極偏壓時元件是在導通的狀態。JFET 則無法做出增強型的元件。

(圖8)是NMOS在飽和區的典型轉換特性曲線。

## (四) 場效電晶體的應用

FET 和BJT 一樣,可以用作開關或放大器,利用閘極的電壓訊號,控制源極和汲極間的電流。 JFET 和MOSFET 使用的場合略有不同。JFET 可用作類比開關及訊號放大器,特別是低雜訊的放大器,但很少用在數位電路中的邏輯運算及功率放大器;MOSFET 用途較廣,除一般的開關、訊號放大及功率放大器外,在數位電路及記憶體等大型積體電路(VLSI,下一節會介紹)方面,都是MOSFET的天下,特別是將NMOS 及PMOS 製作在同一晶圓,稱做CMOS(complementaryMOS)的技術,或稱互補式金氧半電晶體技術。FET 應用在類比訊號放大器的設計方法和BJT 相當類似。對應BJT 的共射極、共基極和共集極的接法,FET 也有共源極、共閘極和共汲極的接法。FET的汲極不能當作輸入端,閘極不能當輸出端,和BJT 集極與基極的限制也一樣。FET 應該偏壓在飽和區(或恆流區),閘極的電訊號疊加在原來之直流偏壓電壓上,造成輸出電流ID的變化。細節這裡就不再介紹。

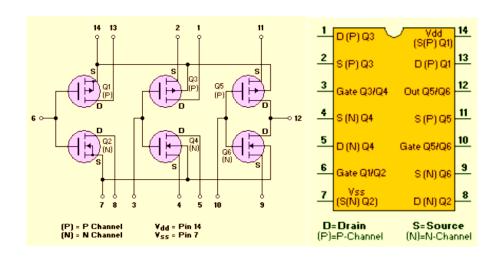

本實驗所用到的 MOSFET 編號是 CD4007UB,屬於 CD4000 系列。CD4000 系列通常是 CMOSFET (即包括 PMOS 和 NMOS 電晶體)。CD4007 的接腳請查閱網頁元件資料。有些電晶體源極(source)已經和基板(substrate)連在一起(CD4007 的接腳  $6 \cdot 7 \cdot 8$ ),有些則沒有連在一起,我們可以根據需要來選擇用哪一個電晶體。

這次實驗所使用的 MOSFET 都是增強型的(enhancement),在 VGS=0 時,他們應該是在截止區(OFF),即源極(source)和汲極(drain)間不導通。

圖 9 (左) CD4007UB 內部電路圖 (右) CD4007UB 接腳圖

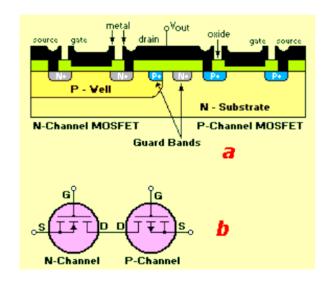

圖 10 N 通道及 P 通道的 MOSFET 在同一基板上的剖面圖(a)及對應的電路符號(b)

### (八) 使用 MOS IC 之注意事項

MOS IC 是非常脆弱的,很容易受到靜電的破壞。你常常發現你只是用手拿了一個 MOS 元件,走到麵包板然後插上,他竟然就壞了!就這麼簡單,MOS 被靜電給幹掉了!

記住!在你將 MOS IC 插入電路前, 先用另外一隻手碰一下電路, 將靜電放掉。

你知道嗎?對電路而言,你的身體好像一個 100pF 的電容和一個幾 K 歐姆的電阻。在較乾燥的天氣,靜電可以把你充電到 10kV,是的!不要懷疑,一萬伏特的電壓在你身上。空氣的游離(崩潰)電壓約 10kV/cm,有時候手指碰到門把前所產生的火花就是靜電使空氣游離所導致的。而 MOS 閘極的崩潰電壓只有不到 100 伏特。

MOS 元件在運送或儲藏時,必須插在導電的泡棉或裝在導電的袋子中。你也必須小心烙鐵和桌上的靜電,常將你自己的身體和處理的電路接地(你和地間最好串接一個  $1M\Omega$  的電阻)。

有一些 MOS 元件會有閘極保護電路的設計,雖然會使得特性表現差一點,但被靜電燒壞的機率卻小很多。有時候,你買到的 FET 接腳上有保護的金屬線或導電橡皮筋,要到 FET 裝在電路後才能拆掉。

#### 資料來源:

- 1. 中興大學 孫允武教授

- 2. http://www.learningelectronics.net/VA3AVR/tutorial/xtor/xtor10/xtor10.html